微电子制造和组件组装是任何射频产品生产链的关键步骤,因为它决定了产品的上市时间以及可以在有限的产品开发时间内进行重新设计周期的次数。 微电子制造是具有挑战性的,因为制造的组件的小尺寸和它可以包括的特性,使得微电子制造容易受到环境,热和电气条件的影响。 了解这些挑战和许多其他挑战,导致微电子工艺工程作为一门独立的学科出现,以应对这一领域的挑战和迅速进步。

从CAD设计开始,最终以工作器件结束,需要遵循许多制造步骤和程序。 对于高产量和高直通率的目标,这些步骤需要彻底验证,以提供一致的结果,从而可以锁定这一特定器件的工艺过程。 工艺实验可以包括材料选择的几个试验,材料层的生长方法,层对层的对齐方法,以及材料图案化方法。从一个制造商到另一个制造商, 每一个都可以是不同的,为任何人创造了大量的空间来发明新的工艺制成技术。 为了应对微电子制造的复杂性,具有不同背景的个人(例如物理、化学、电气、机械工程和材料科学)和最新技术和设备的培训技能通常协同参与工作,以使这一工艺取得成功。

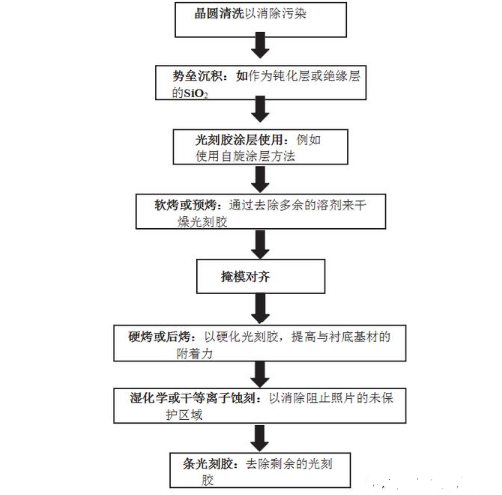

光刻(Photolithography fabrication)是通过光波将图案从版图或掩模转移到半导体晶圆表面的工艺。 图案的转移机制首先使用一种光敏聚合物材料,称为光刻胶图案,其形状定义在掩模上。 一旦图案从掩模转移到光刻胶,然后使用干法或湿法蚀刻方法将图案从光刻胶转移到晶圆的表面。 这个工艺本身由几个步骤组成,需要建立几个工具。 图1所示的图表概述了基本的光刻步骤,并简要地解释了每一步。

晶圆清洗通常是通过一套标准的步骤来进行的,并从将晶圆运行到溶剂中以清洁晶圆表面可能存在的颗粒和有机残留物开始的:

图1、 光刻工艺流程中涉及的基本步骤

接下来,晶片被彻底浸泡在去离子水(DI, deionized water)中,以去除任何剩余的溶剂,然后再进行RCA清洁。 该RCA清洁氧化晶圆提供一层薄的氧化物保护层到晶圆表面。 然后将晶圆浸泡在氢氟酸(HF,hydrofluoric acid)中,以去除晶圆表面的氧化层。 最后,晶圆被DI冲洗,然后用氮气吹干。

薄膜材料的沉积通常采用化学气相沉积(CVD, chemical vapor deposition)或物理气相沉积(PVD,physical vapor deposition)。 作为一个概念,这两种涂层工艺的应用都非常广泛。 半导体制造商通常采用更具体的衍生技术。 PVD使用纯源材料,通过蒸发气化。 PVD热供应是通过应用大功率电或激光烧蚀来完成的。 然后,蒸发材料将通过真空扩散到基片衬底表面,以产生所需的薄膜。 然而,CVD不需要纯源材料,但该材料与挥发性前体混合作为材料载体。 然后,在一定温度下,通过气体输送系统将涂层材料注入包围衬底基片的反应室。 然后,蒸气物质与底物反应并最终沉积在其上。 在这个阶段,前驱体材料分解并离开沉积在衬底中的材料。 CVD工艺比PVD工艺需要更高的温度。 根据应用的不同,因为几个工艺制成方面的因素,如工艺复杂性、所需的薄膜厚度、原材料的可用性和成本原因,一种方法可能比另一种方法更好。 为此,在清洗晶圆后,屏障或钝化层,如二氧化硅(SiO)2 通常沉积在晶圆的表面。

然后,利用标准自旋涂层技术将光刻胶层应用于晶圆的表面,通过每分钟几千轮(RPM)高速旋转的晶圆基板产生离心力,能够均匀地将光刻胶层分布在晶圆表面。 根据对外加光的反应,光刻胶可分为正抗蚀剂或负抗蚀剂。 在正抗蚀剂中,暴露在外加光下的抗蚀剂是可溶解的部分,因此可以通过光刻胶显影液去除,而未暴露的抗蚀剂部分仍然不溶。 负光刻胶的作用方式与正抗蚀剂相反。 在这两者之间,正抗蚀剂变得更加流行,因为它们为小几何特征提供了相对更好的过程可控性。

其次,软烘焙被用来去除所有溶剂后,光刻胶涂层工艺,在那里光刻胶变得光敏,因此软烘焙是决定光成像质量的关键步骤。

在应用第一个光掩模后,每个后续掩模必须与前一个掩模对齐,以便能够准确地将图案转移到晶圆表面。 掩模对准是使用掩模和晶圆上的对准标记来在光暴露前登记图案。 一旦掩模对齐,光刻胶就会通过具有高强度光源的图案掩模曝光,从而形成预期的图案。

其次,在光刻过程中,硬烘焙步骤是必要的,以硬化所开发的光刻胶,并提高与晶片表面的附着力。

硬烤可能是不必须的工艺,而软烘焙是需要的,如在金属提升模式。

然后将不需要的光刻胶材料和残留物蚀刻掉,从而在晶圆表面形成图案。 模式转移到晶圆表面可以使用三种方法之一:减法转移(刻蚀)、添加剂转移(选择性沉积)和杂质掺杂(离子注入)。 减法采用湿化学或干等离子体刻蚀,这是最常用的模式转移方法。 然而,干式蚀刻对湿式蚀刻提供了相对更多的轮廓控制。

要在掩模上印刷和图案化小特征,需要根据方程(1)来使用波长较短的光源:

方程(1)

上式中R是分辨率,NA是确定光源可以发出光的角度范围的孔径数值,而λ是施加光的波长。

衬底基板是基本的建筑结构,用于提供机械支持和电气连接到在几乎任何射频电路中的电子元件中。 在决策过程中,在为特定应用选择合适的衬底技术时,除了制造成本和与特定制造技术的兼容性外,还必须考虑电气、机械、化学和热参数等几种材料性能。 无论基板是共烧陶瓷(例如氧化铝)、PCB(例如FR4)或半导体基板,事先了解材料性能对于了解基板和导体的不同性能是如何影响到特定设计的性能是至关重要的。

共烧陶瓷基板在介电材料纯度和许多其他性能方面有着广泛的品种。 陶瓷基板适用于高容量生产,可用于高微波频率(高达50G Hz~),这取决于导体和介电材料在损耗方面的选择。 共烧陶瓷可用于高密度射频互连线,支持有源和无源元件,并提供非常可靠的密封封装解决方案,具有广泛的好处,包括防止潮湿,热,热膨胀,机械冲击和腐蚀等。 陶瓷多层基板也有利于在层压板内实现嵌入式电感和电容器,因此在给定的设计中可以减少表面安装组件的数量。 共烧陶瓷的两种主要类型是低温共烧陶瓷(LTCCs,low temperature co-fired ceramics)和高温共烧陶瓷(HTCCs, high temperature co-fired ceramics)。 两种类型的烧结的温度的区别大约是900○ 用于LTCC和1500○为HTCC。 与HTCC相比,LTCC所需的较低温度是由于事实上LT CC有较高的玻璃含量,使得能在较低的温度上结合陶瓷晶粒。 LTCC也被称为玻璃陶瓷,因为除了少量的结合剂外,玻璃还与特定成分的氧化铝混合,以产生均匀的化合物。 LTCC和HTCC都是为了构造一个与金属共烧的多层陶瓷基板而制造的。 在金属化方面,LTCC在低于金属熔点的温度下使用高导电材料的金属组成,如铜、金或银。 然而,HTCC使用电阻率相对较高的金属,如钨、钼或钼锰,在高温下共烧,以支持机械刚性和长期可靠性非常重要的应用。

在LTCC或HTCC中,多层基组分的生产首先通过铸造陶瓷复合材料来产生均匀厚度的金属片。 然后,金属片被图案化,并根据给定设计的布局使用冲床来创建孔洞。 然后,三维(3D)结构是由二维(2D)片构成的,其中通孔填充通常使用厚膜丝网印刷工艺。 陶瓷多层衬底的制备在加工顺序上不同于半导体衬底。 在半导体制造中,层被依次加工在彼此的顶部;而在陶瓷制造过程中,每一层被单独图案化,然后堆叠和共烧,以建立均匀的多层结构。

LTCC和HTCC技术的关键区别包括:

● 与HTCC相比,LTCC具有较低的介电常数和较低的损耗

● HTCC具有较高的温度和机械稳定性

● LTCC具有较高的金属导电性

● LTCC层数较高;

● LTCC制造周期较短;

● LTCC使用相对低成本的工具。

采用低成本阻燃4(FR4,flame retardant 4)材料的PCB基板是由玻璃增强环氧树脂制成的,适用于低频应用。 FR4介质材料的损耗角正切是限制其高频应用的一个限制因素。 其他PCB基板,如罗杰斯(Rogers)的层压板,提供低损耗材料,可使用高达20GHz,合理的插入损耗。 柔性和有机多氯联苯也是可用的,它们的使用主要与可穿戴医疗设备以及机器人等轻量级移动设备有关。 陶瓷基板在具有较低的热膨胀系数方面优于PCB基板,可以在较高的温度下工作,能够实现密封封装,提供更好的热性能、更好的高频性能,并通过在多层基板中嵌入无源元件以实现较小的封装尺寸来实现高的集成密度。

下面的讨论在一定程度上强调了不同的半导体衬底技术,这些技术主要与RFICs和MICs的制造相关。 半导体衬底材料分为元素半导体和化合物半导体两大类:.

● 单元素半导体,在元素周期表的IV族中发现,如硅(Si)。

● 化合物半导体可进一步分为三个亚类:.

– 二元素化合物由III-V族元素(如GaAs和AlP)和II-VI组元素(如ZnS)组成。

– 三元素化合物由III-V族元素形成,如InGaAs和AlGaAs等。

– 四元素化合物由III族和V族中的四个元素组成,如InGaAsP。

由于传统的Si光刻工艺的成熟,Si晶圆基板是半导体制造中用于实现大多数RFICs的主要材料。 另一种在特定应用中获得牵引力的衬底材料是砷化镓(GaAs),它在MMIC中的应用更为突出。 GaAs是一种半绝缘衬底,其元件具有较低的电容损耗和导体损耗。GaAs被开发并用于集成电路制造,以克服Si基板器件在高频使用时遇到的工作频率限制。 与Si相比,GaAs材料的高电子迁移率使GaAs在高速电路中处于有利地位。 然而,高昂的制造成本限制了其经济可行性。 硅锗(SiGe) 是将Si制造的加工成熟度、集成水平和成本效益与GaAs等更昂贵技术的速度和性能相结合的另一种半导体技术。 与Si技术制造的晶体管相比,SiGe基晶体管的电流、噪声和功率能力有了显著的提高。 SiGe非常适合需要高频工作(GHz频率范围)和高速通信电路(如数据转换器)的应用领域。 预计未来几年,SiGe的市场份额将增加,特别是随着5G网络的部署和对大规模互联网连接的需求。 然而,目前,SiGe正面临来自替代技术的高度竞争。

纯硅基板是一种低电阻材料,对块体Si基器件的金属结构造成介质损耗。 因此,在Si衬底上实现的无源组件比在GaAs衬底上实现的无源组件具有更低的Q值。对低功耗微电子技术的需要推动了几种晶圆衬底技术的发展,以在块体Si衬底和器件金属层之间实现绝缘,如蓝宝石上的硅(SOS,silicon on sapphire)和绝缘体上的硅(SOI, silicon on insulator)。

SOS是20世纪60年代发展起来的一种晶圆基板技术,是生产高速低功耗器件的途径。 其中SOS的主要优点之一是具有优良的线性性能,这是大功率RFFE(射频前端)模块的关键要求。 然而,SOS的可制造性是一个限制因素,因为形成具有最小结晶缺陷的Si层主要困难阻碍了大批量生产的潜力,因此也阻碍了SOS器件产品商业化的潜力。 美国公司Peregrine半导体公司最近的发展极大地改善了蓝宝石晶片上Si薄膜的结晶特性,为RFIC器件制造商今后可能采用和考虑铺平了道路。 本质上,SOS衬底是利用外延生长在蓝宝石衬底上沉积Si膜而产生的。 反过来,这将产生结晶缺陷,因为晶格不匹配蓝宝石。 这一缺陷是通过在Si膜内植入Si离子来消除Si膜在与蓝宝石衬底的界面上的结晶效应,并将其转化为非晶态条件。 在热处理和氧化环境下,Si膜被再结晶形成。然后去除剩余的SiO2 薄膜以获得所需的SOS衬底。

SOI衬底的基本结构是在顶部薄Si层和块体Si衬底之间形成SiO2 层,而器件是建立在其中的。 在芯片制造中,SOI晶片衬底技术被认为是一个进化的步骤,与SOS等其他技术相比具有几个优势。 主要优点是器件金属层与衬底之间的寄生电容降低;因此,可以获得更好的电气性能。 例如,SOI衬底通常用于制造射频开关的基于场效应的晶体管(FETs)减少源和漏到衬底的电容,而这反过来又对开关隔离、速度和插入损耗产生显著影响。 此外,SOI衬底技术在温度上的性能变化较小,与大多数传统的制造工艺兼容,不需要特殊的培训和设备来制造。

最常见的SOI晶片的制造工艺是通过注入氧(SIMOX,separation by implantation of oxygen)进行分离,形成块状硅支撑晶圆之上的电绝缘SiO2 层。 其他应用使用通过注入氮气(SIMNI,implantation of nitrogen)进行分离,其中氧气被氮气或氧气和氮气(SIMON)的组合所取代,而不产生任何不利影响。所有的SIMOX、SIMNI和SIMON工艺都有很好的能力精确控制氧化层的厚度。 氧或氮离子被离子束注入硅中。 离子束的能量决定了绝缘层的深度以及后续硅覆盖层的厚度。

虽然SOI技术正在成为IC行业面临的几个技术挑战的答案,但超薄SOI层的生产以建立器件的体Si与掩埋氧化物层之间的低轮廓以及厚度均匀性仍然是一个突出的挑战。 此外,由于氧化层的热导率低(SiO2 为0.4W/m-K,如果与纯块状Si相比(Si为150W/m-K)),SOI可能会受到自热效应的影响。