在过去五十多年中,从肖克莱等人发明第一个晶体管到超大规模集成电路出现,硅半导体工艺取得了一系列重大突破,使得以硅材料为主体的CMOS集成电路制造技术为主流,逐渐成为性能价格比最优异、应用最广泛的集成电路产业。

如果说在亚微米/深亚微米(Sub-Micron)时代,器件的主要bottleneck在热载流子效应(HCE: Hot Carrier Effect)以及短沟道效应(SCE: Short Channel Effect)。那么在纳米(or Sub-0.1um)时代,随着器件特征尺寸的缩小,器件内部pn结之间以及器件与器件之间通过衬底的相互作用愈来愈严重,出现了一系列材料、器件物理、器件结构和工艺技术等方面的新问题,使得亚0.1微米硅集成电路的集成度、可靠性以及电路的性能价格比受到影响。这些问题主要包括:

(1) 体硅CMOS电路的寄生可控硅闩锁效应以及体硅器件在宇宙射线辐照环境中出现的软失效效应等使电路的可靠性降低;

(2) 随着器件尺寸的缩小,体硅CMOS器件的各种多维及非线性效应如表面能级量子化效应、隧穿效应、短沟道效应、窄沟道效应、漏感应势垒降低效应、热载流子效应、亚阈值电导效应、速度饱和效应、速度过冲效应等变得十分显著,影响了器件性能的进一步改善;

(3) 器件之间隔离区所占的芯片面积随器件尺寸的减小相对增大,使得寄生电容增加,互连线延长,影响了集成度及速度的提高。

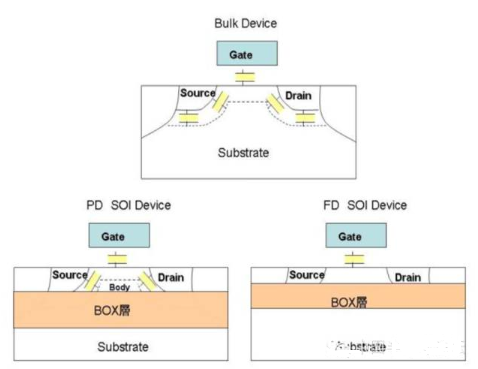

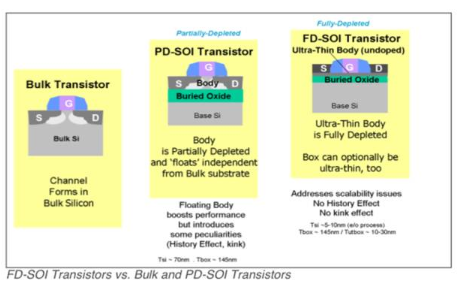

虽然深槽隔离(STI->DTI, Deep Trench Isolation)、电子束刻蚀、硅化物、中间禁带栅电极等工艺技术能够降低这种效应,但是只要PN结存在就会有耗尽区,只要有Well就会有衬底漏电,所以根本无法解决。所以绝缘衬底上硅(Silicon-On-Insulator,简称SOI)技术以其独特的材料结构有效地克服了体硅材料不足,以前最早是在well底部做一个oxide隔离层,业界称之为BOX (Buried OXide),隔离了well的bulk的漏电,但是这种PN结依然在well里面,所以PN结电容和结漏电还是无法解决,这种结构我们称之为部分耗尽型SOI (PD-SOI)。后来继续演进发展到减薄oxide上面的Silicon厚度(UTSi: Ultra-Thin Si),使得它和PN结深度一样,这样PN结底部的耗尽层就不见了,这就是传说中的全耗尽型SOI (FD-SOI)。目前,主流的纳米制程技术都必须要采用FD-SOI技术,比如最近IBM的7nm技术就是要用SOI加上SiGe来抑制short channel effect。

讲到SOI,最早的前身应该是SOS(Silicon on Sapphire, 蓝宝石上硅),那个年代主要用于宇宙航天等电子器件(Satellite system),防止宇宙射线照射(radiation)导致器件失效,为啥用蓝宝石主要是因为它是一种氧化铝单晶结构,可以用它的(1-102)晶面上用异质外延方法生长一层外延层单晶硅。但是由于价格太贵无法民用商业化(commercial),后来到1980年代逐渐被SOI取代。

所以,如何在BOX(Buried OXide)上长一个Si来形成SOI wafer是一个技术挑战,我们前面讲了如果要形成单晶层你的底部必须是单晶,如果SOS当然也可以,如果是Oxide肯定就不行了。怎么办?如何制备SOI wafer?业界了解到的就如下三种:

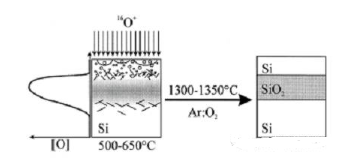

1) 注氧隔离 (SIMOX: Separation by Implantation of Oxygen),通过高剂量(~E18 氧离子/cm2)的氧离子通过高能量(200KeV)注入到Si下面,然后通过Post implant anneal来反应形成~400nm的BOX (Buried OXide)。

SIMOX做出来的SOI具有比较好的BOX均匀性,能够通过注入能量控制BOX上面Si的厚度。但是注入退火的温度影响Si的微结构(microstructure)。所以退火温度一般选择~600C。

还有个问题是BOX厚度太薄会导致SOI与衬底击穿短路,起不到隔离效果,所以需要一道Internal OXide (ITOX)来长一层OX (~1350C),而一部分氧会穿过Si进入到Si/BOX界面反应生成ITOX来提高BOX厚度。

2) 键合法(Wafer bonding/mounting):将两个氧化的Si晶片键合在一起,通过后续的热处理减小键合应力。也叫layer transfer。

3) Smart Curt法:大家自己百度吧。

SOI的制程会带来很多优点,如减小短沟效应(SCE)、减小亚阈值漏电(subthreshold leakage, off-current)、提高饱和电流(on-current),所以它能提供了更高速(结电容变小)、低功耗的性能(低漏电)。当然SOI也有它固有的寄生特性:

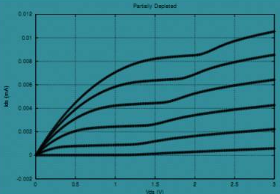

1) 最典型的为kink-effect,也叫作floating-body effect (浮体效应),因为SOI的well都是floating在substrate里面,所以它的well是没有接电压的,当漏极的反偏pn结流过电流时,会使硅外延层的电位提高,从而增加了沟道电导,故随着漏电压的增大,漏电流也增大,形成非饱和特性,从而降低了漏极击穿电压性能(https://en.wikipedia.org/wiki/Floating_body_effect)。而且浮体效应会导致阈值电压的浮动、记忆效应、迟滞效应等一些列问题。当然衬底接出会解决这个问题,但是会增加面积以及增加体电阻。

2) 其次就是自加热效应(self-heating effect),因为我们底部和周边都是用Oxide隔离(DTI和BOX),而oxide的导热性不好,所以载流子碰撞产生的热量被聚集在well里,会减小载流子寿命。在Id-Vd特性曲线里饱和区曲线会略微下降,而不是微微上升。(自己google或baidu吧)

PD-SOI和FD-SOI的区别?为啥不直接用FD-SOI技术?

因为FD-SOI的开启电压对BOX上的Si厚度非常敏感(10mV/nm),所以在特定的领域还是会使用PD-SOI来解决Vt的variation问题。但是FD-SOI的Subthreshold亚阈值特性比PD-SOI好很多(<65mv>

现在很多8寸的0.18um/0.13um以下的BCD和RF制程已经开始导入SOI制程平台或SOC (system on chip)来集成RF和高速度和低功耗特性,未来的物联网(IoT)应该也是SOI的主流市场(无线通讯和低功耗),只是制程瓶颈在于成本和复杂度。